观看B站视频JT写的

一,阻抗匹配

1,需要阻抗匹配的信号环境

如果信号传输的时间除以信号上升时间(或者下降时间)这个比值超过10%就对这个传输线进行阻抗匹配.

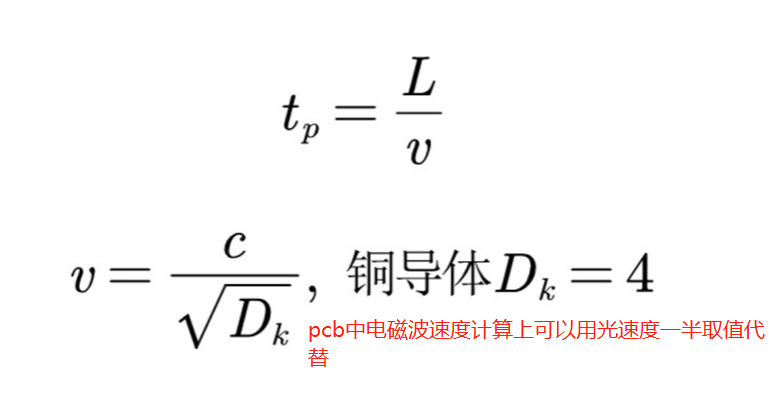

2,传输时间tp等于导线长度除以信号的速度,

电信号在真空中的传播速度大约是30万公里每秒,即3×10^10 cm/s(^表示幂运算),亦即约11800 mil/ns.

在其他介质中,假设相对介电常数为Er,则传播速度为 11800/Er^0.5 mil/ns;

例如在水中,水的相对介电常数是80,所以传播速度是真空中的1/9,即11800/(80^0.5) mil/ns;

一般PCB板FR4材料的介电常数是4左右,所以,电信号在其中的传播速度大约是11800/(4^0.5) = 5900 mil/ns。

假如PCB的FR4材料介电常数为4.3,则电信号传输速度为:11800/(4.3^0.5) =5700mil/ns

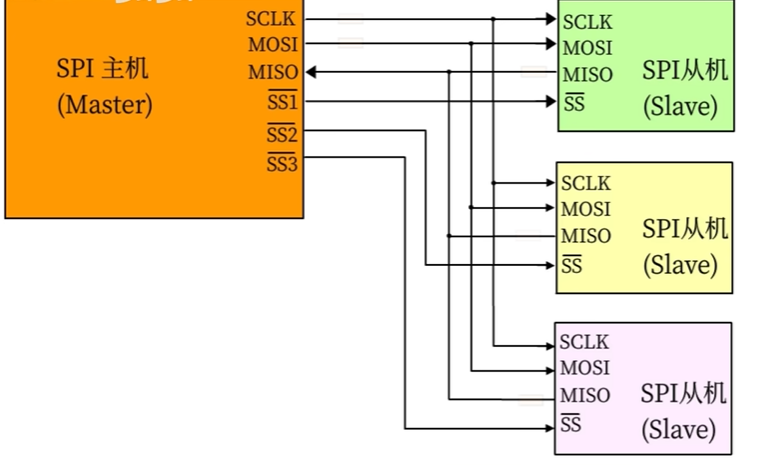

二,spi

这种从来不放电阻也没有什么问题,遇到这种人,我这种半桶水解释不了.

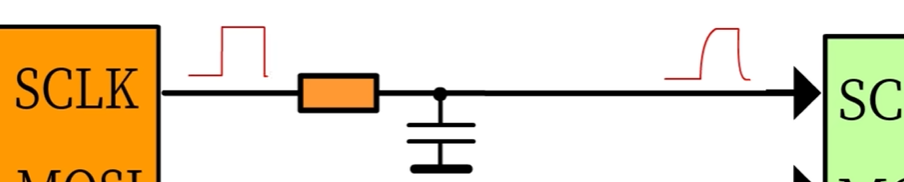

但是PCB中存在分布电容信号就会一定程度的失真,方波变成了一定程度的曲线,组成了一个低通滤波器,延长了上升和下降的时间.

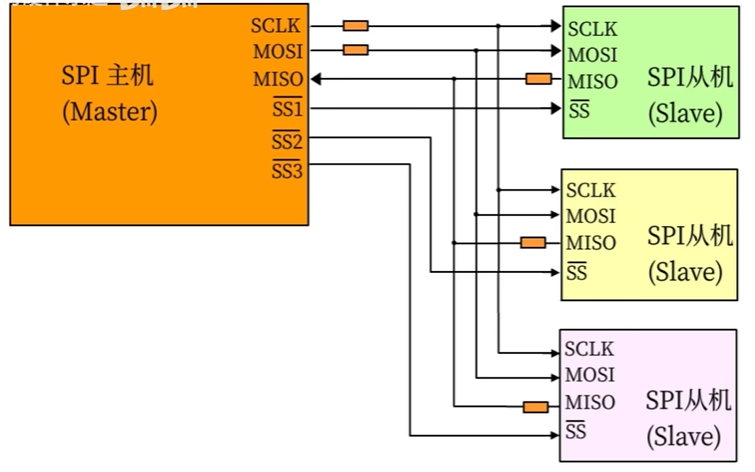

这个时候就需要阻抗匹配啦,但是SPI速度不是固定的没有办法做PCB的时候做整条线的阻抗参数,spi速度是根据从机器件有多快他就跑多快.

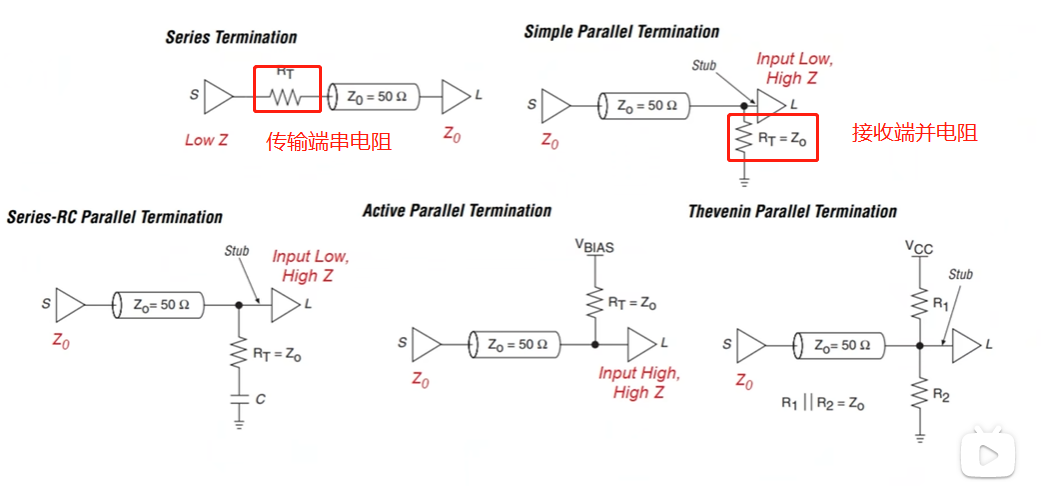

常见的用法是传输端串电阻或者接收端并电阻,然后spi的走线还需要按照高速板走线.

如果传输线的特性阻抗为50欧,串联的电阻可以用22欧或者33欧,与输出内阻相加会接近50欧.

观看别人家的spi模块(ADV模块LTC2380-16)

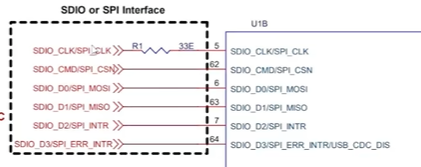

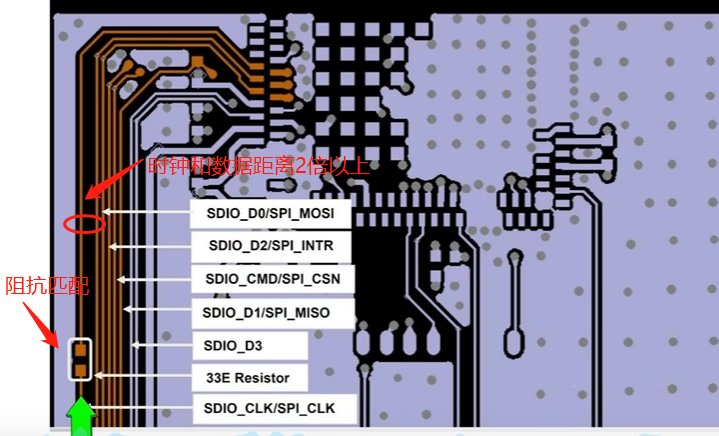

这里就时钟做了阻抗匹配,看一下他们的手册

机器翻译如下

1. SDIO/SPI线的特性阻抗应为50 Ω。

2. 数据与时钟的长度差在100 mils以内。

3. 时钟与数据走线要隔开2倍宽以上的距离。

4. 不要在时钟线的上方或下方不平行的走线

5. SPI走线相邻的层上有良好的地平面。

6. SPI走直线减少转弯和过孔不允许有线头。

然后观察建议的pcb走线

三,USB

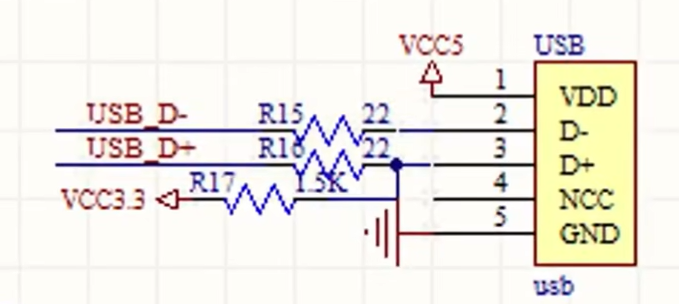

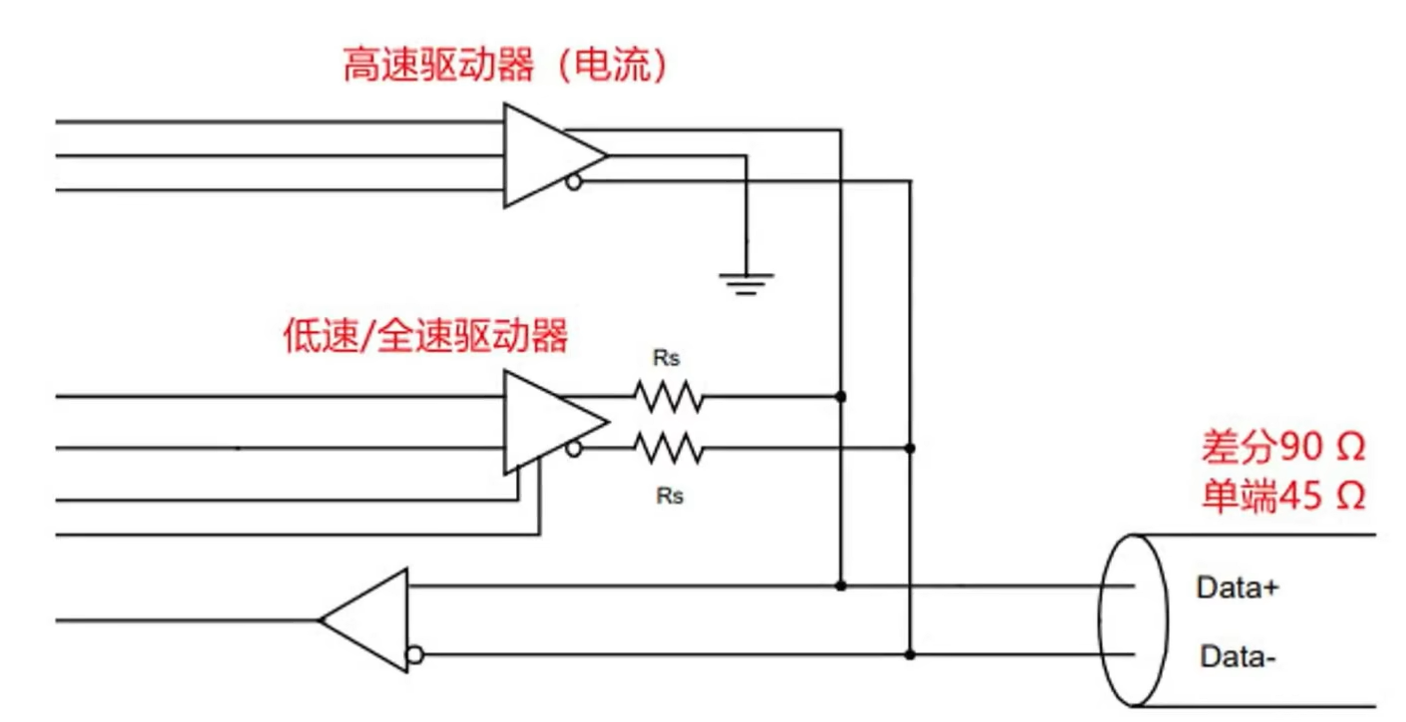

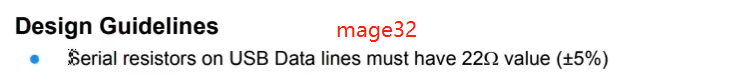

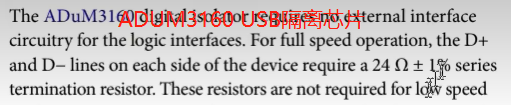

USB的D-,D+两条数据线串了两个电阻,有的是22欧,有的是33欧,有的是0欧,还有直连的,我们先观察波动期试验了解一下阻抗匹配的意义.

波动实验器(电池波也是一种波具有波的属性)

1,当两种密度(不同密度代表不同阻抗)的波动试验器接在一起,在交接处有波的反射

2,波动器尾部悬空,相当于传输线一端开路,到达终端的波很明显的反射回来了

3,终端接一个负载,反射的波形会很小,波的能量绝大部分被负载吸收.

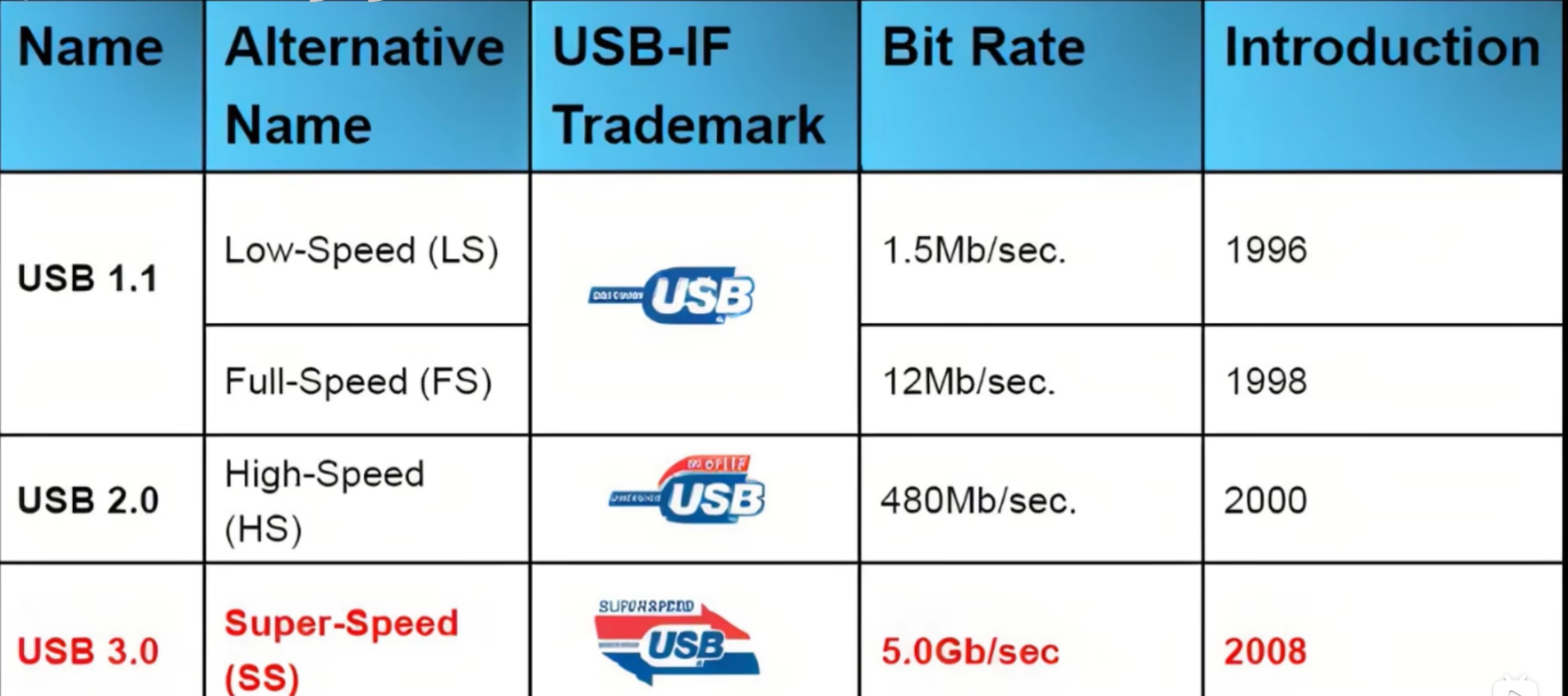

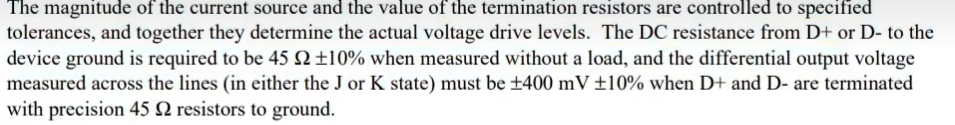

USB标准

英文是说高速USB线要有45欧的阻抗,非高速要28欧到44欧之间

驱动器内阻几乎没有45欧这么大,这个时候为了阻抗匹配就需要串一个电阻啦,所以经常看到USB不同的串联电阻是因为驱动器内阻不同(内助多大看说明书).

例:

这样我们经常看到USB串联的电阻不同就能理解啦,有牛逼的厂家已经把这个电阻做到晶圆上了,(注意晶圆上的电阻占空间很大,这个空间可以放很多半导体,所以不放的很多)但是stm32的USB就不需要

放0欧是为了调试,因为有的pcb走线阻抗匹配不一样做的成功.

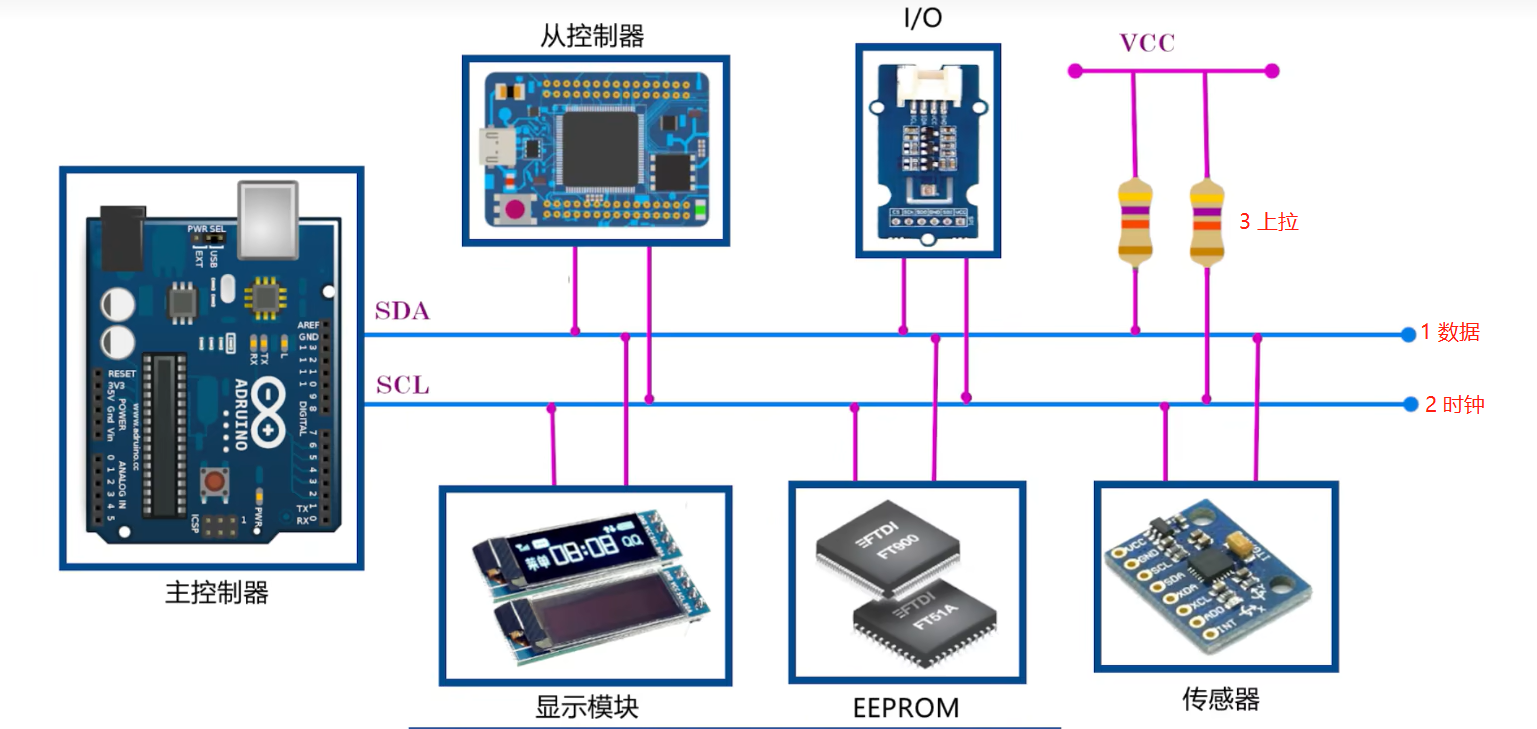

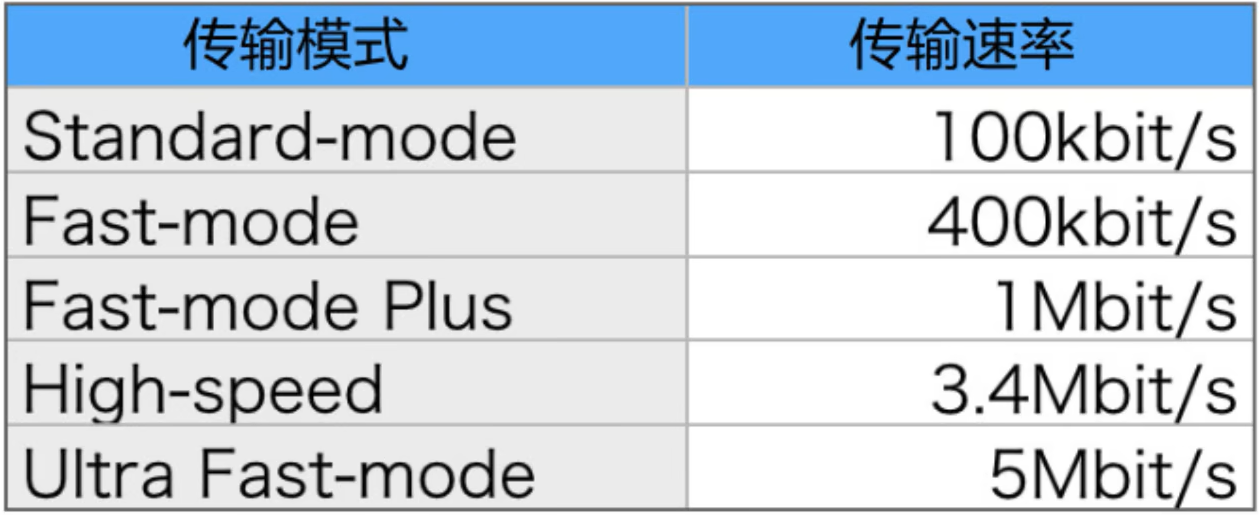

四,IIC总线.

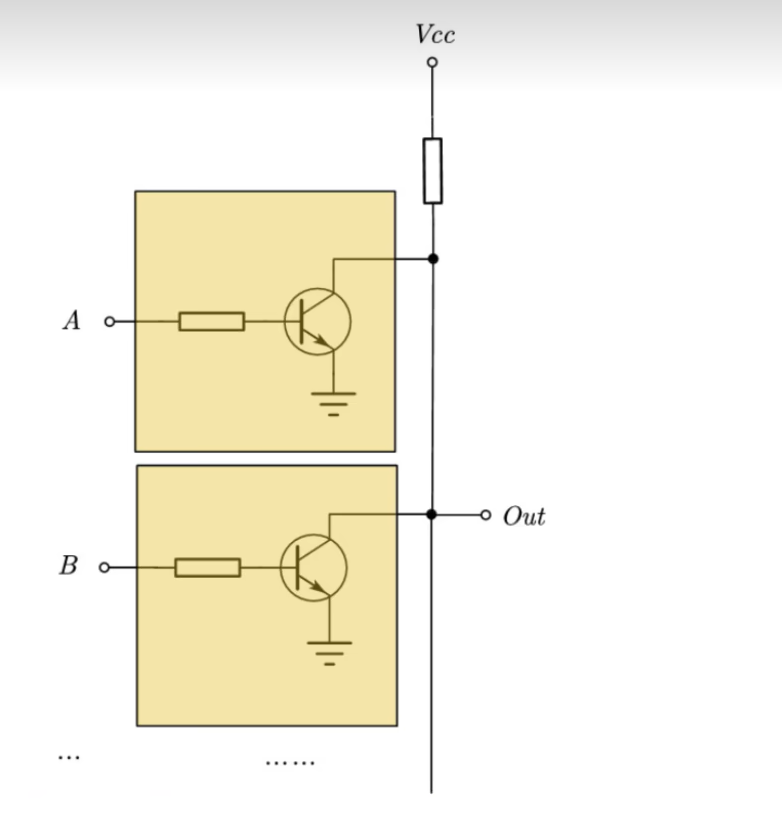

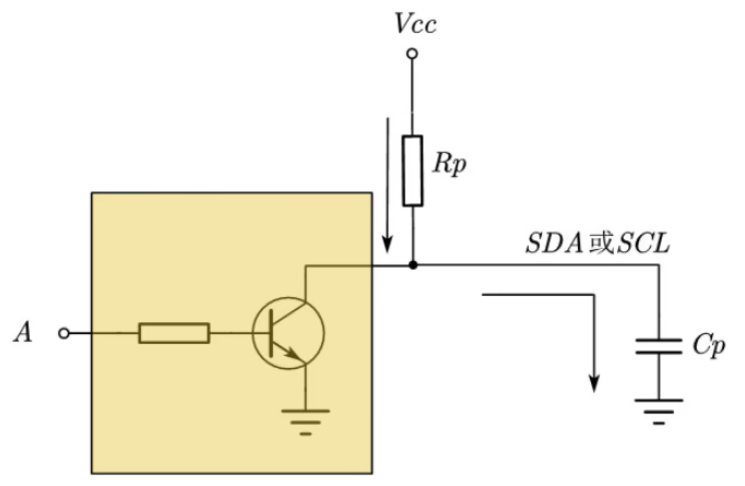

Iic总线不是推挽,而是集电极上拉的模式,这是一种历史悠久的技术,有一定的好处

实际中总线上的信号并不是理想的方波,因为pcb上的布线存在分布电容,总线上的设备有输入电容,于是上拉电阻和这些电容决定了信号的上升沿和下降沿时间.

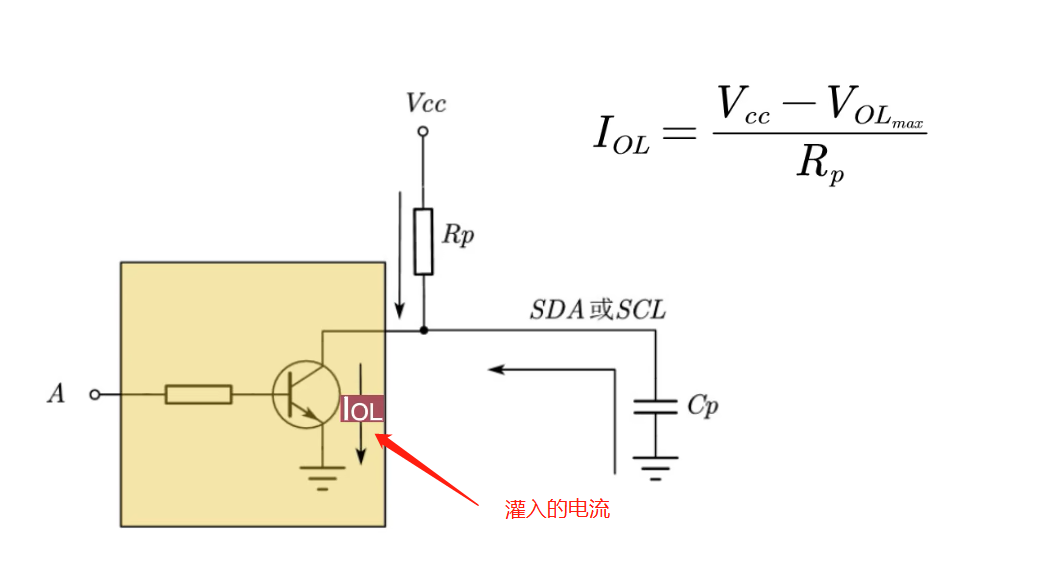

输出低电平,当总线设备拉低输出低电平时电流经过Rp灌入驱动器三极管的集电极,灌入的电流还包括负载电容Cp的放电电流.当Cp放完电的时候就是输出0电平的时候.

这样就能计算上拉电阻Rp的最小值了

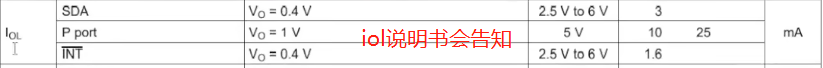

器件说明书也会告知iol和vol的值

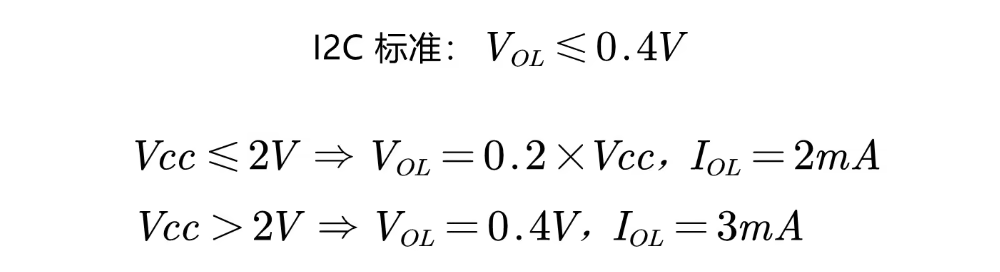

也可以按照通用标准取值

如果供电电压是3.3V的时候,这个上拉电阻最小可以是1k(966Ω)

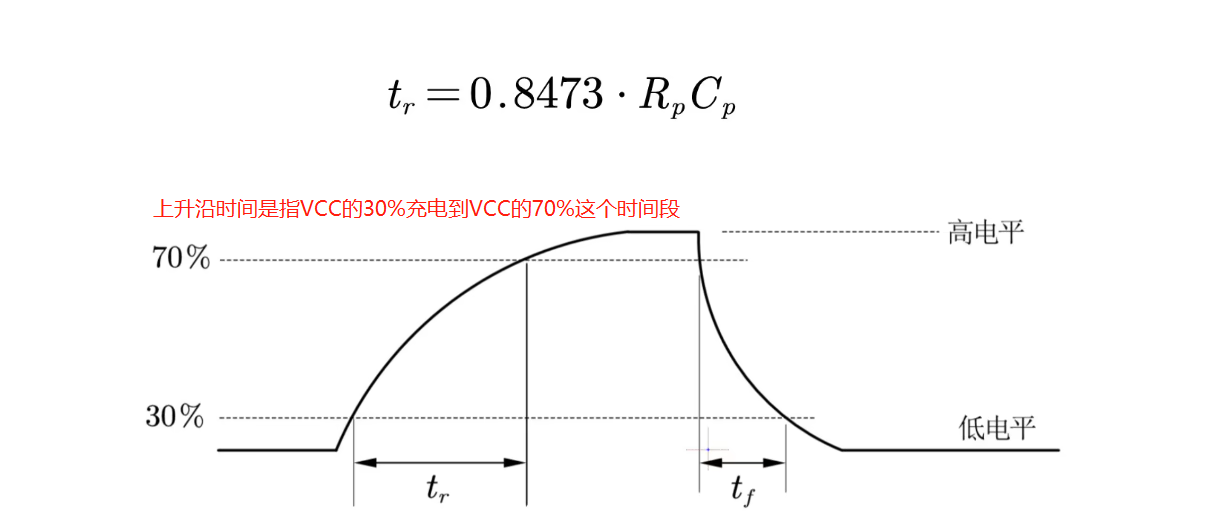

输出高电平,IIC电流输出高电平的时候,驱动电路属于截止状态,VCC 直接对Cp充电,逐渐拉高数据线电平直到电容充满电.上升沿速度由Rp乘以Cp决定

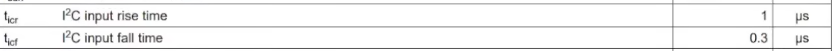

芯片是手册会给出上升沿Tr和下降沿Tf的时间的

Cp值也给出,Iic总线上的容性负载值

![]()

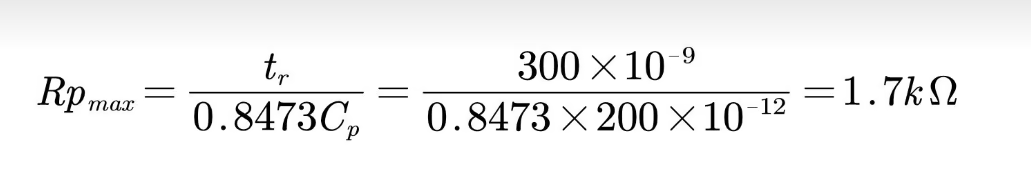

当快速模式下,上升沿时间300纳秒, Cp为200Pf来计算

这样上拉电阻的上限为1.7kΩ

于是我们就可以计算出IIC总线上拉电阻的取值为1k到17k之间,这个时候就可以用不同的阻值来观察示波器时钟的波形,选取一个合适的就行.

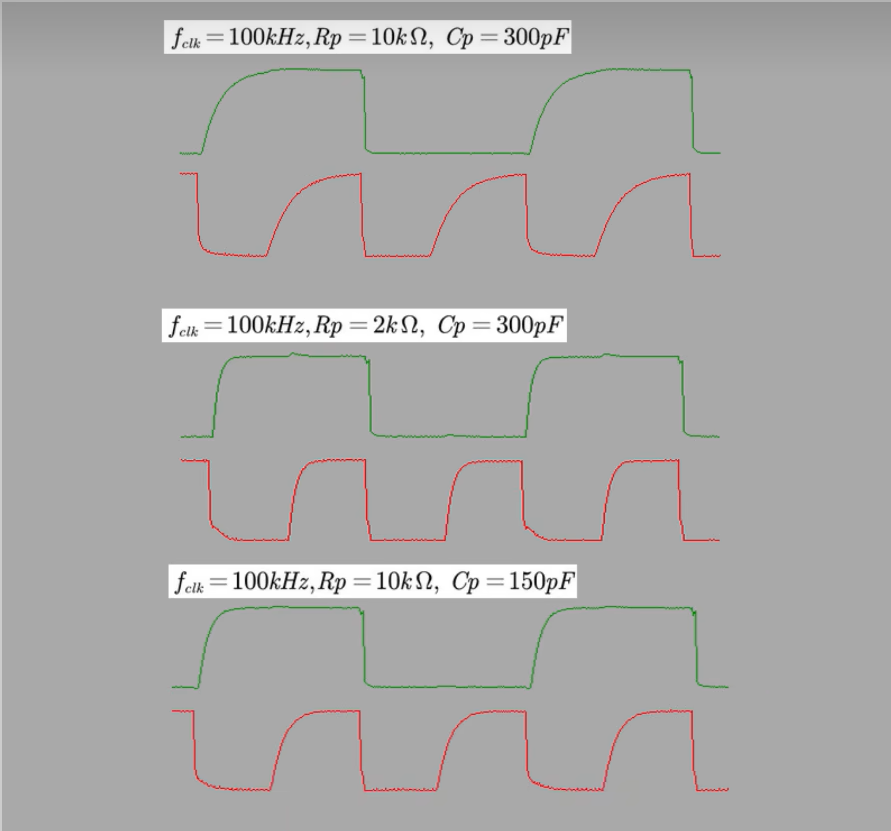

以下是调试截图