IPC-2221标准 继续阅读“线宽和间距”

IPC-2221标准 继续阅读“线宽和间距”

DDR3的信号

控制线:

1,ODT:片上终端使能,ODT使能和禁止片内终端电阻。

2,ZQ:输出驱动校准的外部参考引脚,此引脚应该外接一个 240欧的电阻到VSSQ 上,一般是直接接地了。

3,RESET:复位引脚,低电平有效。 继续阅读“补充知识DDR3的信号”

| 信号类型 | 阻抗要求 | 技术说明 |

|---|---|---|

| DDR3 单端 | 40-50Ω | 数据/地址线(需等长布线,±10%) |

| DDR3 差分时钟 | 80-100Ω | CK+/CK-(动态阻抗匹配优先) |

| DDR4 单端 | 48Ω ±10% | 支持更高频率(≥2400MHz) |

| DDR4 差分时钟 | 96Ω ±8% | 严格时序控制(建议TDR校准) |

| DDR5 单端 | 40Ω ±10% | 支持4800MHz+,需参考完整地平面 |

| DDR5 差分时钟 | 90Ω ±5% | 低电压摆幅(POD逻辑) |

一、什么是 PCB 设计中的 EMC电磁兼容 和 EMI 电磁干扰?

1、EMC 电磁兼容

EMC 是电磁兼容的简称。PCB 中的 EMC 是电路板在其电磁环境中工作而不会对周围的其他设备产生难以忍受的电磁干扰的能力。 继续阅读“知乎收集的电磁兼容”

1,地是回流路径,不是真正的大地,只有形成回路才有电流的流动.

#include “stdio.h”

//加入以下代码,支持printf函数,而不需要选择use MicroLIB

//#define PUTCHAR_PROTOTYPE int fputc(int ch, FILE *f)

#if 1

#pragma import(__use_no_semihosting)

//标准库需要的支持函数 继续阅读“printf函数”

对于crc16,crc32或者其他多项式的校验,只需要更改uint8_t POLYNOMIAL和uint8_t crc行的初始值即可

多项式为:100110001(简记为0x31),也就是CRC-8

将CRC寄存器(8-bits,比生成多项式少1bit)赋初值 继续阅读“CRC”

EEPROM 继续阅读“常见基本电路”

阻抗的定义:在某一频率下,电子器件传输信号线中,相对某一参考层,其高频信号或电磁波在传播过程中所受的阻力称之为特性阻抗,它是电阻抗,电感抗,电容抗……的一个矢量总和。

设计 COUPON注意事项:

1)保护线与阻抗线之间距需大于阻抗线宽 。

2)阻抗线长度一般设计在 6-12INCH范围内。

3)相邻信号层之最近 GND 或POWER 层为阻抗测量之接地参考层。

4)两 GND 及POWER 之间所加信号线的保护线不可遮蔽到 GND及 POWER 层之间任一层信号线。

5)为保证镀铜的均匀性,需在外层空板位加抢电 PAD 或铜皮

1,需要做阻抗的线

通讯协议,接口,信号点对点的延时大于六分之一的上升沿等. 继续阅读“阻抗计算,SI9000”

当电路板上功率元件突然启动的时候,单片机重启了, 需要串个二极管给单片机再接 继续阅读“瞬态抑制二极管”

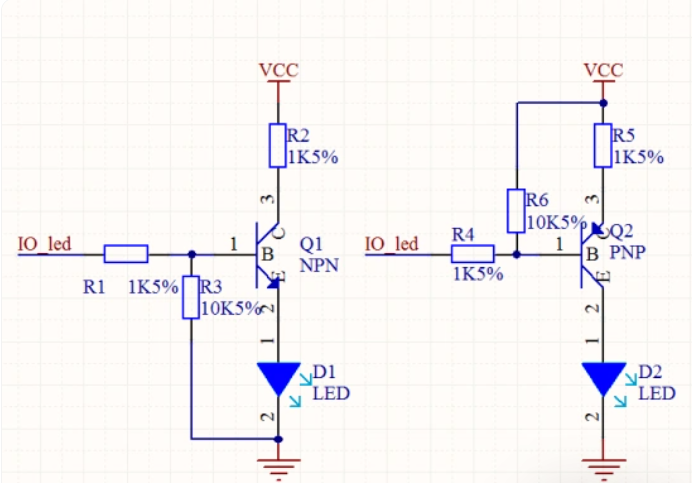

看不懂,后两张是叶子帮忙注释了

//P_SW1 &= ~(1<<5);

//P_SW1 |= (1<<4);

//这样写就是把 P_SW1 的第5位置0 第4位置1

1B(Byte 字节)=8(bit位),

1KB (Kilobyte 千字节)=1024B,

1MB (Megabyte 兆字节 简称“兆”)=1024KB,

1GB (Gigabyte 吉字节 又称“千兆”)=1024MB, 继续阅读“位的换算”

网上收集整理,后面慢慢增加,看到写的感觉能用的就收集起来,不知道是否合理,反正没有具体想法的时候就先试试。

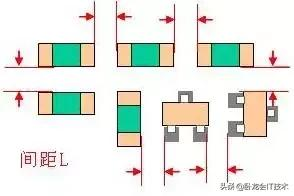

1、贴片之间的间距

贴片元器件之间的间距是工程师在layout时必须注意的一个问题,如果间距太小焊膏印刷和避免焊接连锡难度非常大。

距离建议如下 继续阅读“PCB注意事项”

(1)VCC:C=circuit 表示电路的意思, 即接入电路的电压

(2)VDD:D=device 表示器件的意思, 即器件内部的工作电压;

(3)VSS:S=series 表示公共连接的意思,通常指电路公共接地端电压

(4)VEE:负电压供电;场效应管的源极(S)

(5)VBAT:当使用电池或其他电源连接到VBAT脚上时,当VDD 断电时,可以保存备份寄存器的内容和维持RTC的功能。如果应用中没有使用外部电池,VBAT引脚应接到VDD引脚上。