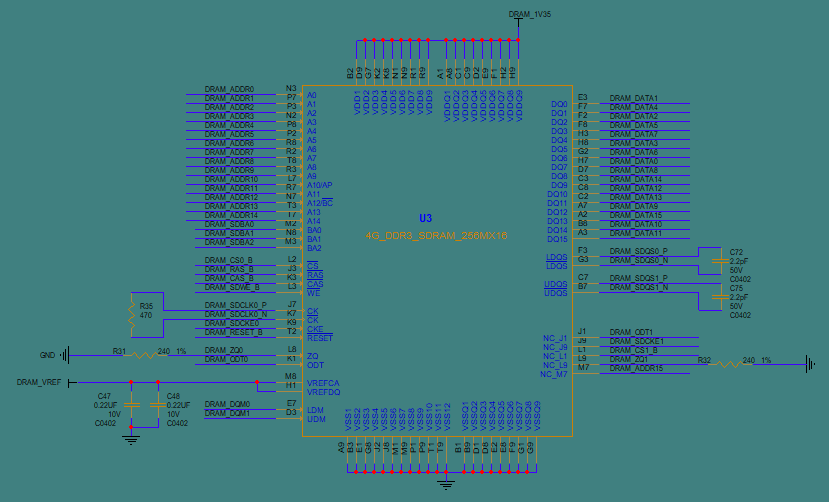

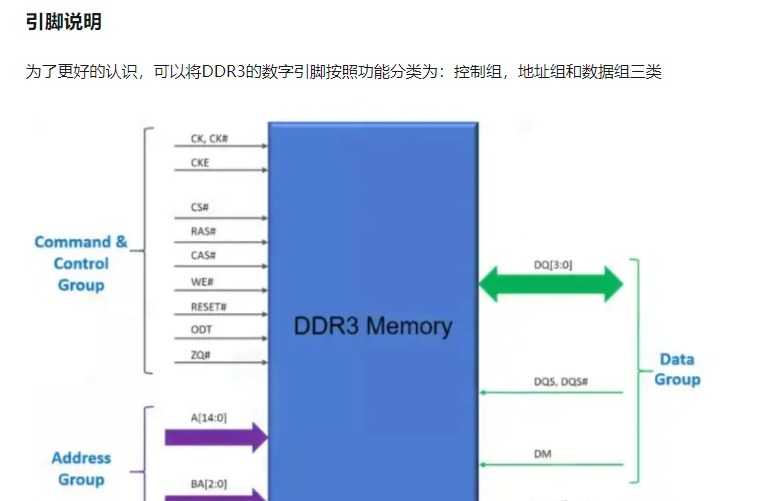

DDR3的信号

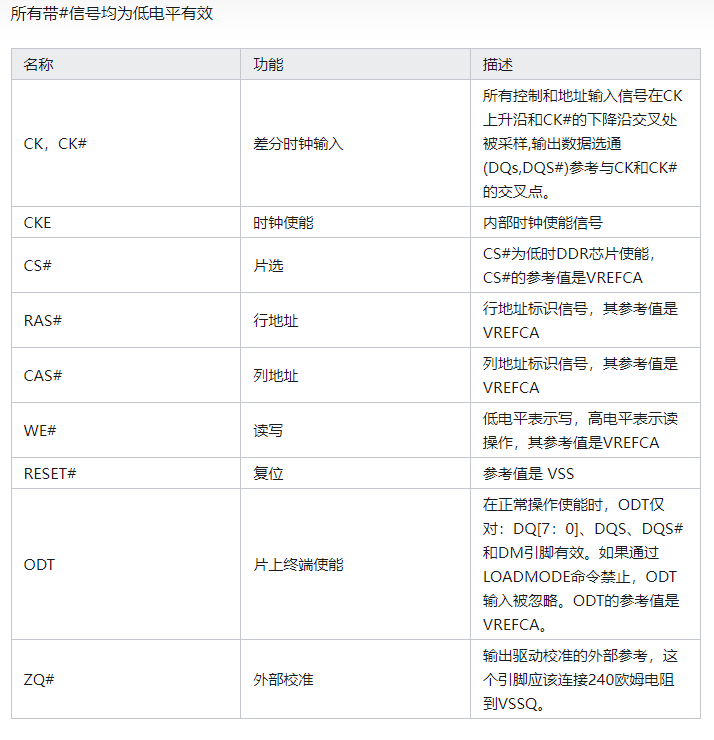

控制线:

1,ODT:片上终端使能,ODT使能和禁止片内终端电阻。

2,ZQ:输出驱动校准的外部参考引脚,此引脚应该外接一个 240欧的电阻到VSSQ 上,一般是直接接地了。

3,RESET:复位引脚,低电平有效。

4,CKE:时钟使能引脚。

5,A12:A12是地址引脚,但是有也有另外一个功能,因此也叫做 BC引脚,A12 会在 READ和 WRITE 命令期间被采样,以决定 burst chop是否会被执行。

6,CK和 CK#:时钟信号,DDR3 的时钟线是差分时钟线,所有的控制和地址信号都会在 CK

对的上升沿和 CK#的下降沿交叉处被采集。

7,CS#:片选信号,低电平有效。

8,RAS#、CAS#和WE#:行选通信号、列选通信号和写使能信号。

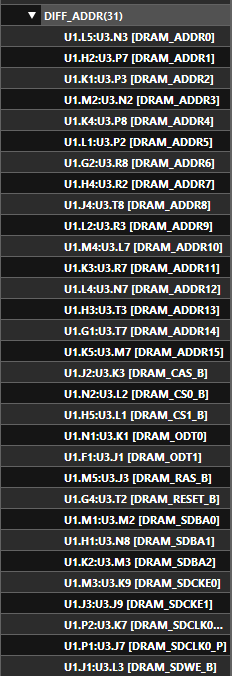

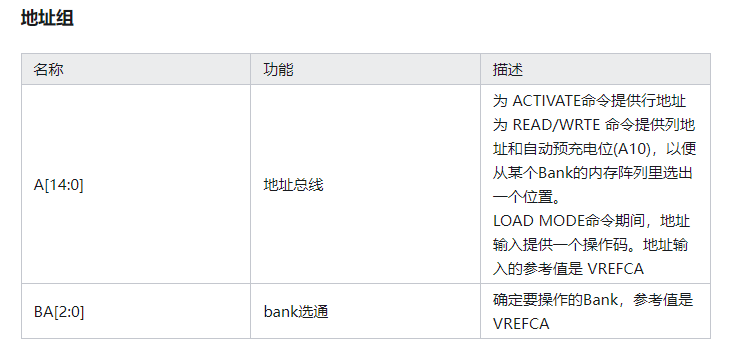

地址线:

9,A[14:0]为地址线,A0~A14,一共15 根地址线,根据NT5CC256M16ER-EK 的数据手册可

知,列地址为 A0~A9,共 10 根,行地址为 A0~A14,共 15 根,因此一个 BANK 的大小就是2^10*2^15*2=32MB*2=64MB,一共有 8个 BANK,因此DDR3L的容量就是 64*8=512MB。

BANK选择线:

一片DDR3有8个BANK,因此需要 3个线才能实现 8个 BANK 的选择,BA0~BA2就是

用于完成 BANK 选择的。

BANK区域:

DDR3 一般都是 8个BANK 区域。

数据线:

因为是16 位宽的,因此有 16根数据线,分别为DQ0~DQ15。

数据选通引脚:

DQS和DQS#是数据选通引脚,为差分信号,读的时候是输出,写的时候是输入。LDQS(有

的叫做DQSL)和LDQS#(有的叫做DQSL#)对应低字节,也就是DQ0~7, UDQS(有的叫做DQSU)

和 UDQS#(有的叫做 DQSU#),对应高字节,也就是DQ8~15。

数据输入屏蔽引脚:

DM是写数据输入屏蔽引脚。

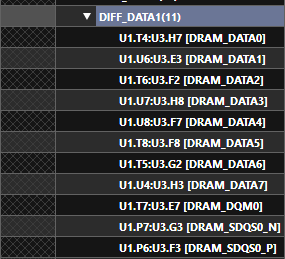

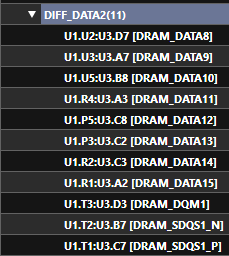

DDR的走线是3组等长,其中2组一信号模一样,DDR走线要求同组同层

8根数据线,1根DM线,1对差分线为第1组

8根数据线,1根DM线,1对差分线为第2组

31根数据线为3组

如果分配不可行就优先保证数据线同组同层

DDR3总共有多种信号线,主要包括数据线、地址线、控制线、时钟线和电源线等。

具体来说,DDR3的信号线可以分为以下几类:

- 数据线(DQ):用于数据传输,通常有16位或32位,具体取决于内存模块的设计。

- 地址线(A0-A14):用于指定内存中的位置。

- 控制线:包括时钟使能信号(CKE)、时钟信号(CK和CK#)、控制信号(如CS、RAS、CAS、WE等)。

- 电源线和地线:提供电力支持和地参考。

在布线时,需要注意以下几点:

- 走线规则:数据线通常走在一层上,信号线间距一般为5mil,线宽为6mil。

- 阻抗控制:数据线、地址线和控制线的阻抗一般为50欧姆,差分时钟对的阻抗为100欧姆。

- 等长处理:组内的信号线要保持等长,以确保信号同步。

这些规则和注意事项有助于确保DDR3内存模块的稳定和高效运行12。

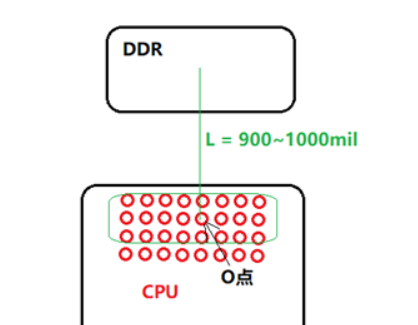

CPU与DDR布局原则

1)一个CPU只对一个DDR时,间距大概900~1000mil,如果中间有串阻,范围1000~1300mil。

2)一个CPU对两个DDR时,两个DDR相对CPU摆放时要严格对称(也是相对O点进行对称)。

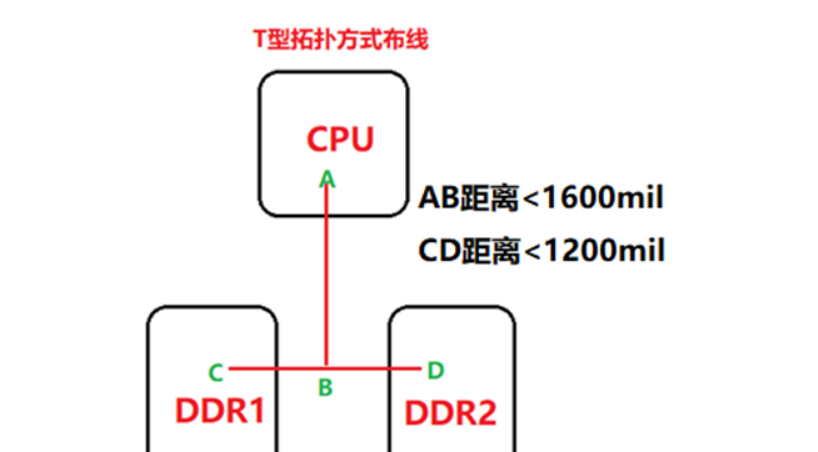

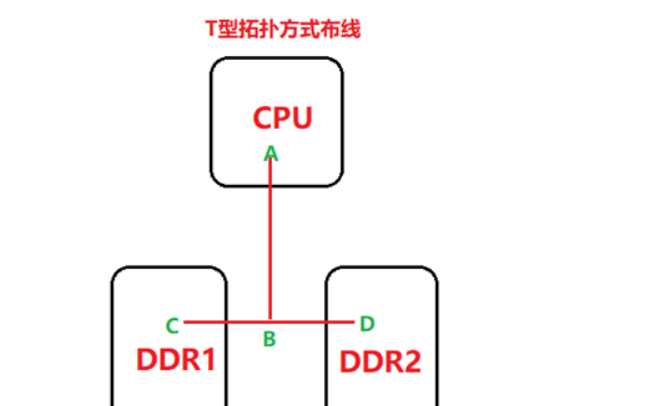

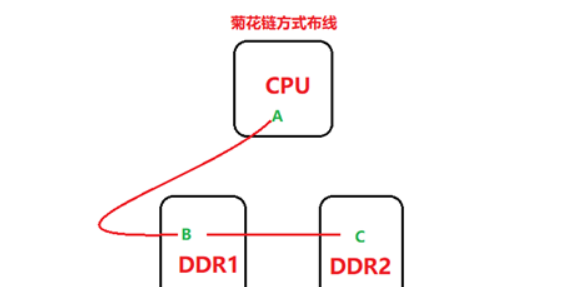

走线方式★

1)点对点:一个CPU仅对一个DDR, 只能用点对点的方式布线。

2)T型:一个CPU对两个DDR或4个DDR,线从A点到B点,B点分支分别到C和D点。

3)菊花链:一个CPU对两个DDR或4个DDR,下图线从A点到B点,B点再到C点。

CS#,RAS#,CAS#和WE#可以构成命令组,它们将在时钟的上升沿被采用,在DDR手册中可以查看对应的真值表。

DDR等长规则

1:数据线以DQS为基准等长,地址线、控制线、时钟线以时钟线为基准等长,若软件中没有以时钟线为基准的,要手动将其选为基准线。

2:数据线最大长度尽量不超过2500mil,组内长度误差范围控制在+/- 25ml,DQS与时钟线长度误差控制在+/-250mil,单片DDR的最大误差不超过1000mil:

3:地址线误差范围控制在+/-100mil:DQS、时钟差分对内误差范围控制在+/-5mil,设计阻抗时,使对内间距不超过2倍线宽。信号实际长度应当包括零件管脚的长度,尽量取得零件管脚长度,并导入软件中。

DDR主要有电源,地,信号线,地址线

先找数据线,优先连接差分对

信号组大致分类

1)地址线、时钟差分、命令控制线,该组信号较多,布线不一定非要走在同一层

2)8根数据高位、1根数据掩码、1对数据锁存差分,共11根线,同一组信号线走同一层。

3)8根数据低位、1根数据掩码、1对数据锁存差分,共11根线,同一组信号线走同一层。

备注:同组信号必须走同一层,不同组信号可走不同层。

4)电源和地